Difference between revisions of "Intel Celeron 300A"

From Vogons Wiki

| (5 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

{{Device Infobox/Begin | {{Device Infobox/Begin | ||

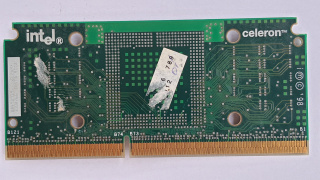

| + | | Image = Intel_Celeron_300A_Top.jpg | ||

| Bus type = FSB | | Bus type = FSB | ||

| Bus width = 64-bit | | Bus width = 64-bit | ||

| Line 15: | Line 16: | ||

| Clock speed = 300 MHz | | Clock speed = 300 MHz | ||

| Arch family = x86 | | Arch family = x86 | ||

| − | | Arch ver = | + | | Arch ver = P6 |

| Endian/Big = N | | Endian/Big = N | ||

| Endian/Little = Y | | Endian/Little = Y | ||

| Line 34: | Line 35: | ||

<gallery mode="packed"> | <gallery mode="packed"> | ||

| − | |||

| − | |||

Image:Intel_Celeron_300A_Bottom.jpg|Rear view | Image:Intel_Celeron_300A_Bottom.jpg|Rear view | ||

</gallery> | </gallery> | ||

| Line 42: | Line 41: | ||

* [http://ark.intel.com/products/27183/Intel-Celeron-Processor-300-MHz-128K-Cache-66-MHz-FSB Intel ARK] | * [http://ark.intel.com/products/27183/Intel-Celeron-Processor-300-MHz-128K-Cache-66-MHz-FSB Intel ARK] | ||

| + | * [http://www.cpu-world.com/CPUs/Celeron/Intel-Celeron%20300A-66.html CPU World] | ||

Latest revision as of 22:46, 2 May 2020

Intel Celeron 300A

| Bus type | FSB |

|---|---|

| Bus width | 64-bit |

| Bus speed | 66 MHz |

| Manufacturer | Intel |

| Chipset | Mendocino |

| Connectors | Unknown |

| Requires -5VDC? | Unknown "Unknown" is not recognized as a Boolean (true/false) value. |

| Requires -12VDC? | Unknown "Unknown" is not recognized as a Boolean (true/false) value. |

| CPU | |

| Socket | Slot 1 |

| Clock speed | 300 MHz |

| Architecture | x86, P6 |

| Endian | Little |

| Register size | 32 bit |

| Addressable memory | 32 bit |

| Driver | N/A |

The Intel Celeron 300A is a revision of the Intel Celeron 300 with the addition of 128 kB of L2 cache.